DM9051: Single Chip SPI Fast Ethernet Controller

Features

• 32 pin QFN Package

• current consumption 102mA + 40mA transformer

• 0.18 µm Process

• Slave SPI I/F with clock speeds up to 50MHz for high throughput applications

• Supports SPI clock mode 0 and 3

• Supports 10BASE-T, 100BASE-TX and 100M Fiber Interface

• Supports IEEE 802.3az Energy Efficient Ethernet (EEE)

• Supports wakeup frame, link status change and magic packet events for WOL

• Temperature Range: 0°C to 70°C and -40° to 85°C

• Integrated 3.3V to 1.8V low noise regulator

• Supports IPv4/TCP/UDP checksum generation and checking

• EEPROM interface to conficure chip settings

• 3.3V I/O with 5V tolerance

• Supports EMI (Class B) and HBM ESD Rating 8KV

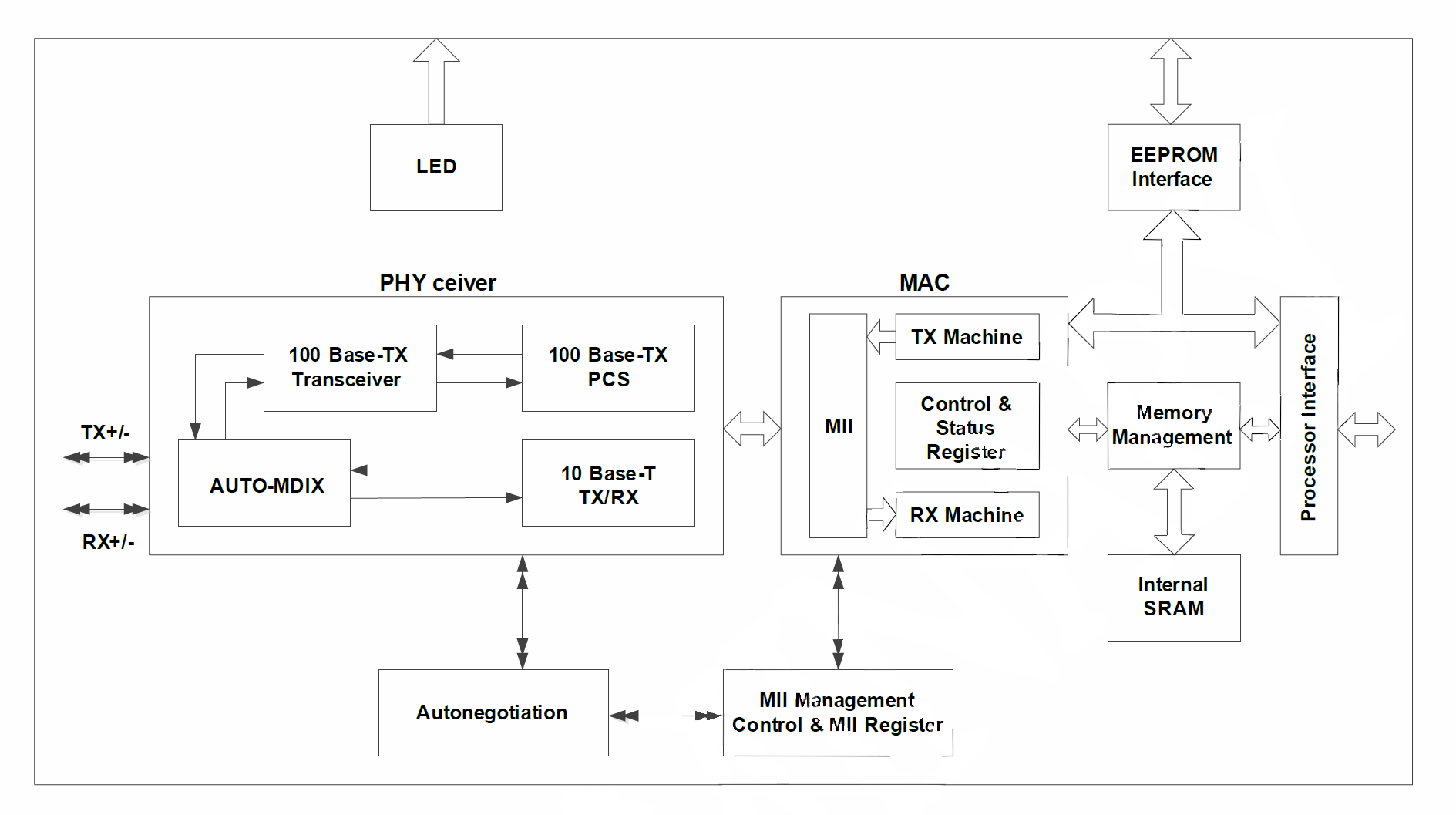

Block Diagam DM9051

The DM9051 is a fully integrated and cost-effective low pin count single chip Fast Ethernet controller with SPI, a 10/100M PHY and MAC, and 16K-byte SRAM. It is designed with low power and high performance process interface that support 3.3V with 5V IO tolerance.

The PHY of the DM9051 can interface to the UTP3, 4, 5 in 10Base-T and UTP5 in 100Base-TX with HP Auto-MDIX. It is fully compliant with the IEEE 802.3u Spec. Its Auto-Negotiation function will automatically configure the DM9051 to take the maximum advantage of its 10M or 100M abilities.

The DM9051 supports IEEE 802.3az in PHY and MAC to save power consumption when Ethernet is idle. The IEEE 802.3x Full-Duplex flow control and Half-Duplex back-pressure function also supported to avoid Ethernet packet loss with link partner.

The slave SPI is designed to support SPI clock mode 0 and 3 that compatible with the all master SPI interface of CPU. The clock speed can up to 50Mhz to co-operation with most high throughput master SPI.

The SPI burst command format is code-effective to minimize the command overhead in access DM9051(I) internal registers and packet data in memory.

General

| 01 Davicom General Layout Guide | 718.85 KB | |

| 02 Davicom Hardware Layout Guide | 9.4 MB | |

| 03 DACOM Ethernet Design-In Guide | 2.64 MB | |

| 04 Connecting two MII devices without transformers | 76.04 KB | |

| 05 Design hint Center-Tabs Transformer to PHY | 305.47 KB | |

| 06 Crystal Information | 58.87 KB | |

| 07 Programming Reference Flow-Chart | 130.04 KB |

Part-Specific

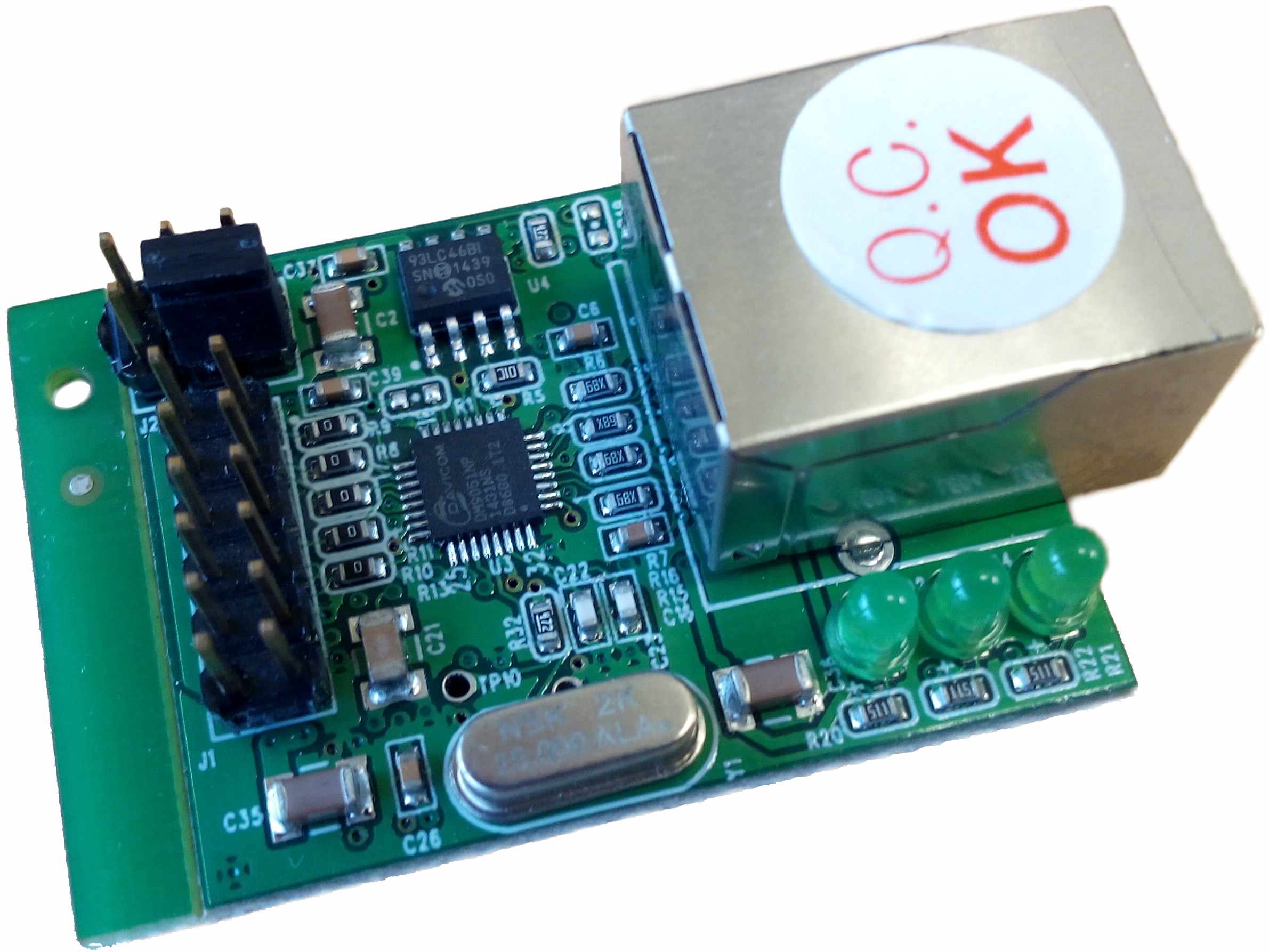

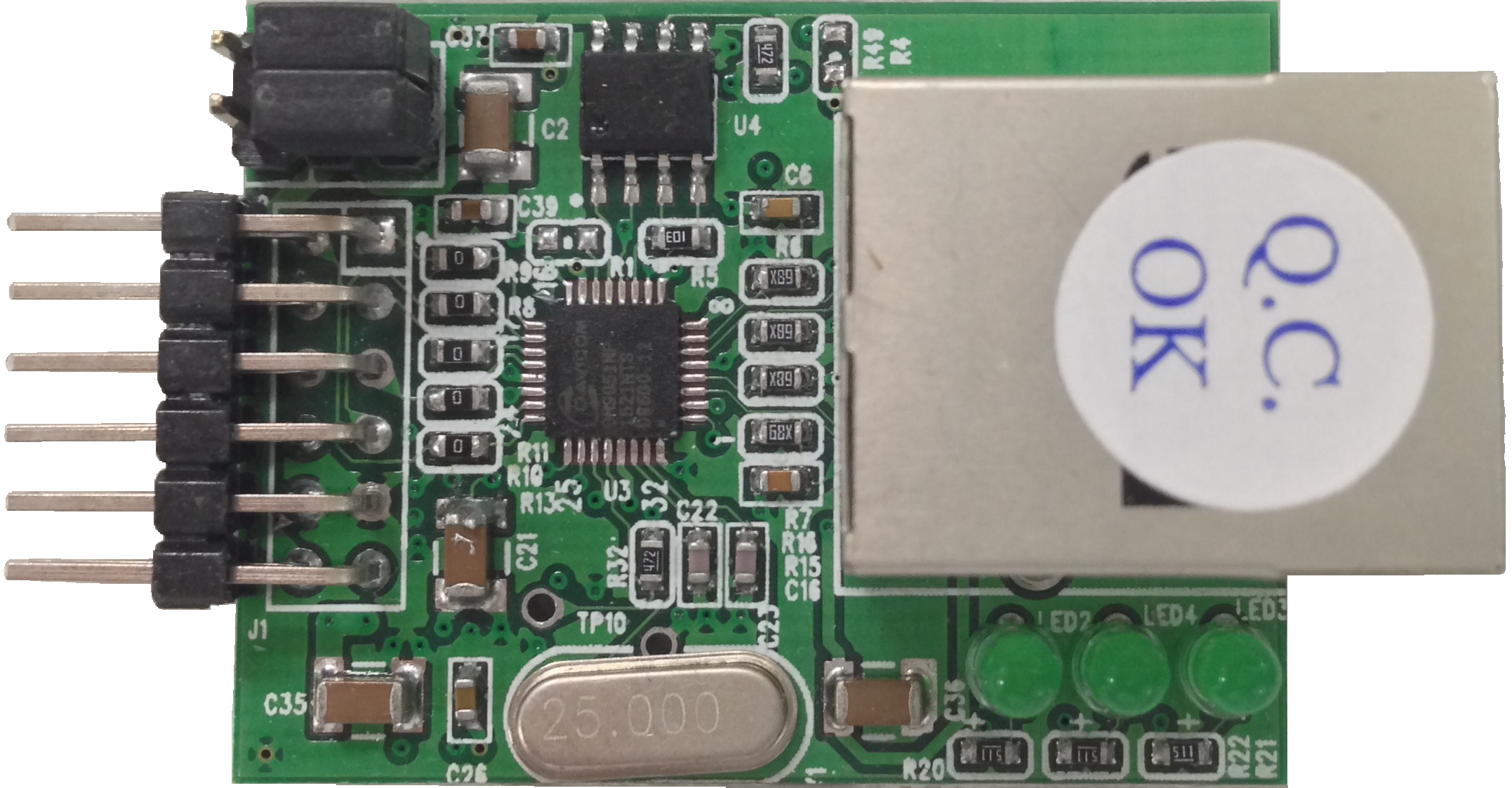

| 11 DM9051 Layout Guide | 248.08 KB | |

| 12 DM9051 Demo Board Schematic | 42.96 KB |

| DM9051(I)-12-MCO-DS-P01_03302015 | 829.02 KB |

Software

| 41 DM9051 Linux Driver 2.2 | 132.1 KB |

| Part-No. | Package | Temperature | Status | Remarks | Customs-Tariff-No. | MSL | Packaging |

| DM9051NP | QFN-32 | 0° to 70°C | active | 85423190 | 3 | 490/Tray | |

| DM9051INP | QFN-32 | -40° to 85°C | active | 85423190 | 3 | 490/Tray |

| 81 Davicom ECN/PCN/EOL Policy | 15.43 KB | |

| 82 PCN Laser Marking | 246.76 KB |

| 91 Soldering Conditions QFP and LQDP pb-free | 38.29 KB | |

| 92 Test Report LQFP pf-free | 100.41 KB | |

| 93 Test Report QFP pb-free | 33.4 KB | |

| 95 LQFP-100 Material Safety Datasheet | 2.45 MB | |

| 94 LQFP-48 Material Safety Datasheet | 442 KB | |

| 96 RoHS CoC 20170113 | 195.92 KB | |

| 97 SONY Green Partner approval | 3.21 MB |