# **DAVICOM Semiconductor, Inc.**

## DM8806/DM8806I

6-Port 10/100Mb Fast Ethernet Smart Switch

DATA SHEET

Preliminary Version: DM8806-M2A-DS-P01

January 18, 2013

## 6-Port 10/100Mb Fast Ethernet Smart Switch

## **CONTENT**

| Gene   | eral Description                                                                                                                                                                                                                                                   | 8             |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Bloc   | k Diagram                                                                                                                                                                                                                                                          | 8             |

| Feat   | ures                                                                                                                                                                                                                                                               | 9             |

| Pin C  |                                                                                                                                                                                                                                                                    |               |

| 1      | Pin Diagram                                                                                                                                                                                                                                                        | 11            |

| 2      | Pin Description                                                                                                                                                                                                                                                    | 12            |

| 4.2.1  |                                                                                                                                                                                                                                                                    |               |

| 4.2.2  |                                                                                                                                                                                                                                                                    |               |

| 4.2.3  |                                                                                                                                                                                                                                                                    |               |

| 4.2.4  |                                                                                                                                                                                                                                                                    |               |

| 4.2.5  | Port 5 GMII/MII Interface                                                                                                                                                                                                                                          | 15            |

| 4.2.6  |                                                                                                                                                                                                                                                                    |               |

| 4.2.7  |                                                                                                                                                                                                                                                                    |               |

| 3      |                                                                                                                                                                                                                                                                    |               |

| Cont   | rol and Status Register Set                                                                                                                                                                                                                                        | 20            |

| 1      |                                                                                                                                                                                                                                                                    |               |

| 2      |                                                                                                                                                                                                                                                                    |               |

| 5.2.1  |                                                                                                                                                                                                                                                                    |               |

| 5.2.2  | Port 0~4 PHY Status Register                                                                                                                                                                                                                                       | 27            |

| 5.2.3  | Port 0~4 PHY Identifier 1 Register                                                                                                                                                                                                                                 | 28            |

| 5.2.4  | Port 0~4 PHY Identifier 2 Register                                                                                                                                                                                                                                 | 28            |

| 5.2.5  | Port 0~4 PHY Auto-Negotiation Advertisement Register                                                                                                                                                                                                               | 29            |

| 5.2.6  | Port 0~4 PHY Auto-Negotiation Link Partner Ability Register                                                                                                                                                                                                        | 30            |

| 5.2.7  | Port 0~4 PHY Auto-Negotiation Expansion Register                                                                                                                                                                                                                   | 31            |

| 5.2.8  | Port 0~4 PHY Specific Control 1 Register                                                                                                                                                                                                                           | 32            |

| 5.2.9  | Port 0~4 PHY Specific Control 2 Register                                                                                                                                                                                                                           | 33            |

| 5.2.10 | Port 0~4 PHY Power Saving Control Register                                                                                                                                                                                                                         | 34            |

| 3      | Switch Per-Port Registers                                                                                                                                                                                                                                          | 35            |

| 5.3.1  | Per Port Status Data Register                                                                                                                                                                                                                                      | 35            |

| 5.3.2  | Per Port Basic Control 0 Register                                                                                                                                                                                                                                  | 35            |

| 5.3.3  | Per Port Basic Control 1 Register                                                                                                                                                                                                                                  | 37            |

| 5.3.4  | Per Port Block Control 0 Register                                                                                                                                                                                                                                  | 39            |

| 5.3.5  | Per Port Block Control 1 Register                                                                                                                                                                                                                                  | 40            |

| 5.3.6  | Per Port Bandwidth Control Register                                                                                                                                                                                                                                | 41            |

|        | Bloc<br>Feat<br>Pin 0<br>1<br>2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>4.2.7<br>3<br>Cont<br>1<br>2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8<br>5.2.9<br>5.2.10<br>3<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.3.5 | Block Diagram |

|    | 5.3.7  | Per Port VLAN Tag Infomation Register                                             | 43   |

|----|--------|-----------------------------------------------------------------------------------|------|

|    | 5.3.8  | Per Port Priority and VLAN Control Register                                       | 44   |

|    | 5.3.9  | Per Port Security Control Register                                                | 46   |

|    | 5.3.10 | Per Port Advanced Control Register                                                | 46   |

|    | 5.3.11 | Per Port Memory Control Register                                                  | 48   |

|    | 5.3.12 | Per Port Discard Limitation Register                                              | 48   |

|    | 5.3.13 | Per Port Energy Efficient Ethernet Control Register                               | 49   |

| 5. | 4 S    | witch Engine Registers                                                            |      |

|    | 5.4.1  | Switch Status Register (210h)                                                     | 50   |

|    | 5.4.2  | Switch Reset Register (211h)                                                      | 50   |

|    | 5.4.3  | Switch Control Register Register (212h)                                           | 51   |

|    | 5.4.4  | CPU Port & Mirror Control Register (213h)  Special Tag Ether-Type Register (214h) | 52   |

|    | 5.4.5  | Special Tag Ether-Type Register (214h)                                            | 52   |

|    | 5.4.6  | Global Learning & Aging Control Register (215h)                                   | 53   |

|    | 5.4.7  | VLAN Priority Map Register (217H)                                                 | 54   |

|    | 5.4.8  | TOS Priority Map 0 Register (218h)                                                | 55   |

|    | 5.4.9  | TOS Priority Map 1 Register (219h)                                                | 55   |

|    | 5.4.10 | TOS Priority Map 2 Register (21Ah)                                                | 56   |

|    | 5.4.11 | TOS Priority Map 3 Register (21Bh)                                                | 56   |

|    | 5.4.12 | TOS Priority Map 4 Register (21Ch)                                                | 57   |

|    | 5.4.13 | TOS Priority Map 5 Register (21Dh)                                                | 57   |

|    | 5.4.14 | TOS Priority Map 6 Register (21Eh)                                                | 58   |

|    | 5.4.15 | TOS Priority Map 7 Register (21Fh)                                                | 58   |

|    | 5.4.16 | MIB Counter Disable Register (230h)                                               | 59   |

|    | 5.4.17 | MIB Counter Control Register (231h)                                               | 59   |

|    | 5.4.18 | MIB Counter Data Low Register (232h)                                              | 59   |

|    | 5.4.19 | MIB Counter Data High Register (233h)                                             | 59   |

|    | 5.4.20 | Special Packet Control 0 Register (234h)                                          | 60   |

| 4  | 5.4.21 | Special Packet Control 1 Register (235h)                                          | 61   |

|    | 5.4.22 | Special Packet Control 2 Register (236h)                                          | 62   |

|    | 5.4.23 | Special Packet Control 3 Register (237h)                                          | 63   |

|    | 5.4.24 | Special Packet Control 4 Register (238h)                                          | 64   |

|    | 5.4.25 | Special Packet Control 5 Register (239h)                                          | 65   |

|    | 5.4.26 | Special Packet Control 6 Register (23Ah)                                          | . 66 |

|    | 5.4.27 | Special Packet Control 7 Register (23Bh)                                          |      |

|    | 5.4.28 | Special Packet Control 8 Register (23Ch)                                          | 68   |

|   | 5.4.29 | QinQ TPID Register (23Dh)                    | . 69 |

|---|--------|----------------------------------------------|------|

|   | 5.4.30 | VLAN Mode and Rule Control Register (23Eh)   |      |

|   | 5.4.31 | VLAN Table - Valid Control Register (23Fh)   | . 71 |

|   | 5.4.32 | VLAN Table - ID_0H Register (250h)           | . 71 |

|   | 5.4.33 | VLAN Table - ID_1H Register (251h)           | . 71 |

|   | 5.4.34 | VLAN Table - ID_2H Register (252h)           |      |

|   | 5.4.35 | VLAN Table - ID_3H Register (253h)           |      |

|   | 5.4.36 | VLAN Table - ID_4H Register (254h)           |      |

|   | 5.4.37 | VLAN Table - ID_5H Register (255h)           | . 72 |

|   | 5.4.38 | VLAN Table - ID_6H Register (256h)           | . 72 |

|   | 5.4.39 | VLAN Table - ID_7H Register (257h)           |      |

|   | 5.4.40 | VLAN Table - ID_8H Register (258h)           | . 72 |

|   | 5.4.41 | VLAN Table - ID_9H Register (259h)           | . 72 |

|   | 5.4.42 | VLAN Table - ID_AH Register (25Ah)           | . 72 |

|   | 5.4.43 | VLAN Table - ID_BH Register (25Bh)           | . 73 |

|   | 5.4.44 | VLAN Table - ID_CH Register (25Ch)           |      |

|   | 5.4.45 | VLAN Table - ID_DH Register (25Dh)           | . 73 |

|   | 5.4.46 | VLAN Table - ID_EH Register (25Eh)           |      |

|   | 5.4.47 | VLAN Table - ID_FH Register (25Fh)           |      |

|   | 5.4.48 | VLAN Table - MEMBER_0H Register (270h)       |      |

|   | 5.4.49 | VLAN Table - MEMBER_1H Register (271h)       |      |

|   | 5.4.50 | VLAN Table - MEMBER_2H Register (272h)       |      |

|   | 5.4.51 | VLAN Table - MEMBER_3H Register (273h)       | . 75 |

|   | 5.4.52 | VLAN Table - MEMBER_4H Register (274h)       |      |

|   | 5.4.53 | VLAN Table - MEMBER_5H Register (275h)       | . 75 |

|   | 5.4.54 | VLAN Table - MEMBER_6H Register (276h)       | . 75 |

|   | 5.4.55 | VLAN Table - MEMBER_7H Register (277h)       | . 76 |

| é | 5.4.56 | VLAN Table - MEMBER_8H Register (278h)       | . 76 |

|   | 5.4.57 | VLAN Table - MEMBER_9H Register (279h)       | . 76 |

|   | 5.4.58 | VLAN Table - MEMBER_AH Register (27Ah)       |      |

|   | 5.4.59 | VLAN Table - MEMBER_BH Register (27Bh)       | . 77 |

|   | 5.4.60 | VLAN Table - MEMBER_CH Register (27Ch)       |      |

|   | 5.4.61 | VLAN Table - MEMBER_DH Register (27Dh)       |      |

|   | 5.4.62 | VLAN Table - MEMBER_EH Register (27Eh)       |      |

|   | 5.4.63 | VLAN Table - MEMBER_FH Register (27Fh)       | . 78 |

|   | 5.4.64 | VLAN Table - Priority Enable Register (290h) | . 78 |

|    | 5.4.65 | VLAN Table - STP Index Enable Register (292h)       | . 78 |

|----|--------|-----------------------------------------------------|------|

|    | 5.4.66 | VLAN Table - Misc_0 Register (293h)                 | 79   |

|    | 5.4.67 | VLAN Table - Misc_1 Register (294h)                 | 79   |

|    | 5.4.68 | VLAN Table - Misc_2 Register (295h)                 | 80   |

|    | 5.4.69 | VLAN Table - Misc_3 Register (296h)                 | 80   |

|    | 5.4.70 | VLAN Table - Misc_4 Register (297h)                 | 81   |

|    | 5.4.71 | VLAN Table - Misc_5 Register (298h)                 | 81   |

|    | 5.4.72 | VLAN Table - Misc_6 Register (299h)                 | 82   |

|    | 5.4.73 | VLAN Table - Misc_7 Register (29Ah)                 | 82   |

|    | 5.4.74 | Snooping Control 0 Register (29Bh)                  | 83   |

|    | 5.4.75 | Snooping Control 1 Register (29Ch)                  | 84   |

|    | 5.4.76 | Address Table Control & Status Register (2B0h)      |      |

|    | 5.4.77 | Address Table Data 0 Register (2B1h)                | 86   |

|    | 5.4.78 | Address Table Data 1 Register (2B2h)                | 86   |

|    | 5.4.79 | Address Table Data 2 Register (2B3h)                | 86   |

|    | 5.4.80 | Address Table Data 3 Register (2B4h)                | 86   |

|    | 5.4.81 | Address Table Data 4 Register (2B5h)                | 86   |

|    | 5.4.82 | Ethernet Address Register 0 for Magic Packet (2B8h) | 87   |

|    | 5.4.83 | Ethernet Address Register 1 for Magic Packet (2B9h) |      |

|    | 5.4.84 | Ethernet Address Register 2 for Magic Packet (2BAh) |      |

|    | 5.4.85 | WoL Control Register (2BBh)                         | 88   |

| 5. | 5 C    | hip Control and Status Registers                    | 89   |

|    | 5.5.1  | Vendor ID Register (310h)                           | 89   |

|    | 5.5.2  | Product ID Register (311h)                          | 89   |

|    | 5.5.3  | Port 5 MAC Control Register (315h)                  | 90   |

|    | 5.5.4  | Fiber Control Register (316h)                       | 91   |

|    | 5.5.5  | IRQ and LED Control Register (317h)                 | 92   |

|    | 5.5.6  | Interrupt Status Register (318h)                    | 93   |

| 4  | 5.5.7  | Interrupt Mask & Control Register (319h)            | 93   |

|    | 5.5.8  | EEPROM Control & Address Register (31Ah)            | 94   |

|    | 5.5.9  | EEPROM Data Register (31Bh)                         | 94   |

|    | 5.5.10 | Monitor Register 1 (31Ch)                           | 95   |

|    | 5.5.11 | Monitor Register 2 (31Dh)                           |      |

|    | 5.5.12 | Monitor Register 3 (31Eh)                           | 96   |

|    | 5.5.13 | Debug Monitor Pin Register (31Fh)                   |      |

|    | 5.5.14 | Memory Access Enable Register (330h)                | 97   |

|    | •      |                                             |       |

|----|--------|---------------------------------------------|-------|

|    | 5.5.15 | Memory Address Register (331h)              | 97    |

|    | 5.5.16 | Memory Dummy Data Register (332h)           | 97    |

|    | 5.5.17 | Memory Read Data Register (333h)            | 97    |

|    | 5.5.18 | Memory Write Data Register (334h)           | 97    |

|    | 5.5.19 | Memory Write Data Low Byte Register (335h)  |       |

|    | 5.5.20 | Memory Write Data High Byte Register (336h) | 98    |

|    | 5.5.21 | System Clock Select Register (338h)         |       |

|    | 5.5.22 | Serial Bus Error Check Register (339h)      |       |

|    | 5.5.23 | Serial Bus Control Register (33Ah)          | 99    |

|    | 5.5.24 | Virtual PHY Control Register (33Dh)         | . 100 |

|    | 5.5.25 | PHY Control Test Register (33Eh)            | . 100 |

|    | 5.5.26 | Disable Port Control Register (399h)        | . 101 |

| 6. | EEPR   | OM Format                                   | . 102 |

| 7. | Funct  | ion Description                             | . 109 |

| 7. | 1 5    | Switch Functions                            | . 109 |

|    | 7.1.1  | Address Learning                            | . 109 |

|    | 7.1.2  | Address Aging                               | . 109 |

|    | 7.1.3  | Packet Forwarding                           | . 109 |

|    | 7.1.4  | Inter-Packet Gap (IPG)                      | . 110 |

|    | 7.1.5  | Back-off Algorithm                          |       |

|    | 7.1.6  | Late Collision                              |       |

|    | 7.1.7  | Half Duplex Flow Control                    | . 110 |

|    | 7.1.8  | Full Duplex Flow Control                    | . 110 |

|    | 7.1.9  | Partition Mode                              | . 111 |

|    | 7.1.10 | Broadcast Storm Filtering                   | . 111 |

|    | 7.1.11 | Bandwidth Control                           | . 111 |

|    | 7.1.12 | Port Monitoring Support                     | . 112 |

|    | 7.1.13 | VLAN Support                                | . 113 |

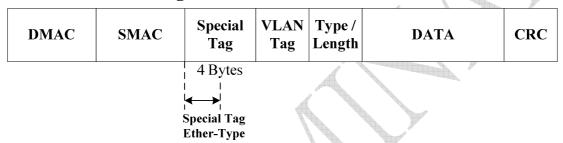

| A  | 7.1.14 | Special Tag                                 | . 114 |

|    | 7.1.15 | Priority Support                            | . 116 |

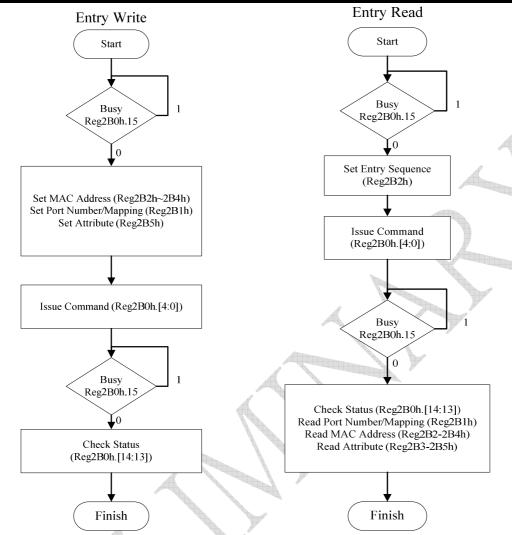

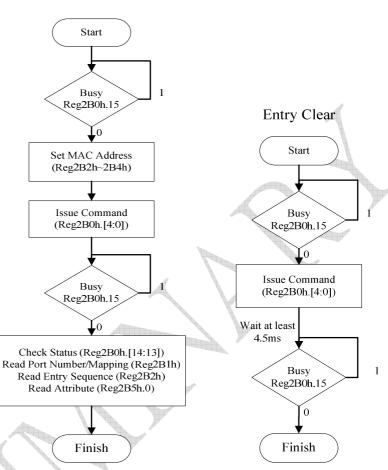

|    | 7.1.16 | Address Table Accessing                     | . 116 |

|    | 7.1.17 | IGMP Snooping                               | . 121 |

|    | 7.1.18 | IPv6 MLD Snooping                           | . 121 |

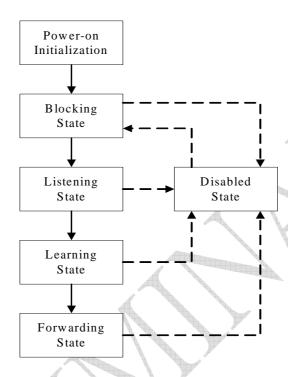

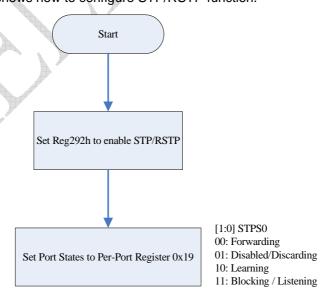

|    | 7.1.19 | STP / RSTP Support                          | . 122 |

|    | 7.1.20 | Port Trunking Description                   | . 124 |

| 7. | 2 I    | nternal PHY Functions                       | . 125 |

| 7.2.1    | 100Base-TX Operation                                             | 125 |

|----------|------------------------------------------------------------------|-----|

| 7.2.2    | 100Base-TX Receiver                                              | 128 |

| 7.2.3    | 10Base-T Operation                                               | 129 |

| 7.2.4    | Collision Detection                                              | 129 |

| 7.2.5    | Carrier Sense                                                    | 130 |

| 7.2.6    | Auto-Negotiation                                                 | 130 |

| 7.2.7    | Auto-MDIX Functional Description                                 | 130 |

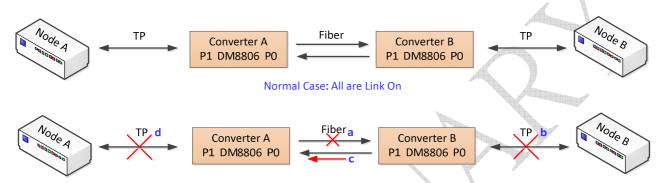

| 7.2.8    | Link Fault Pass-through and Far End Fault Functional Description |     |

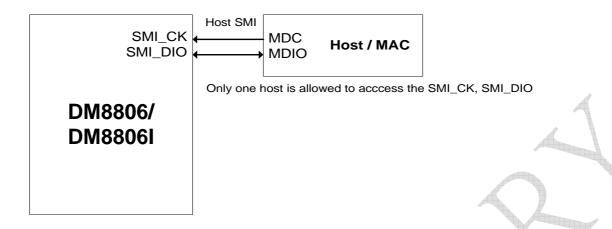

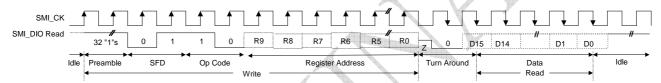

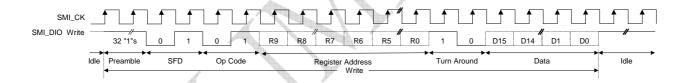

| 7.3      | Host SMI Interface                                               | 132 |

| 7.3.1    | Host SMI Bus Error Check Function                                | 133 |

| 7.4      | LED Mode Control                                                 | 134 |

| 8. DC a  | nd AC Electrical Characteristics                                 |     |

| 8.1      | Absolute Maximum Ratings                                         | 136 |

| 8.2      | Operating Conditions                                             | 136 |

| 8.3      | DC Electrical Characteristics                                    |     |

| 8.4      | AC Characteristics                                               | 138 |

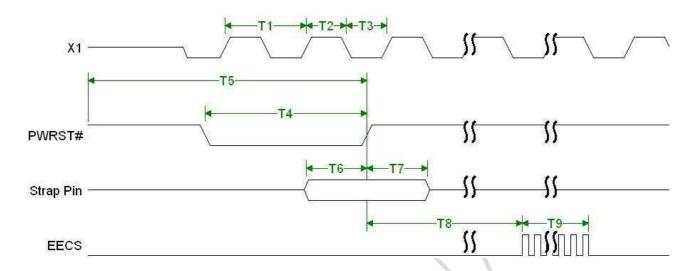

| 8.4.1    | Power On Reset Timing                                            |     |

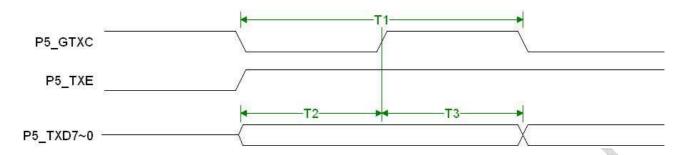

| 8.4.2    | MAC GMII Interface Transmit Timing                               | 139 |

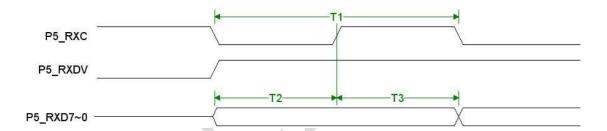

| 8.4.3    | MAC GMII Interface Receive Timing                                | 139 |

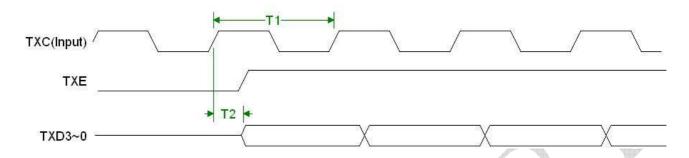

| 8.4.4    | MAC MII Interface Transmit Timing                                | 140 |

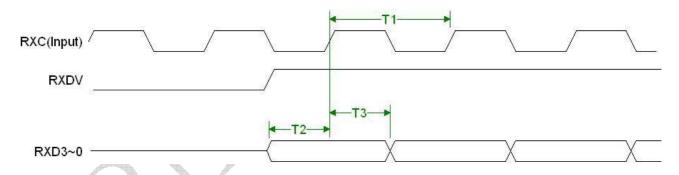

| 8.4.5    | MAC MII Interface Receive Timing                                 | 140 |

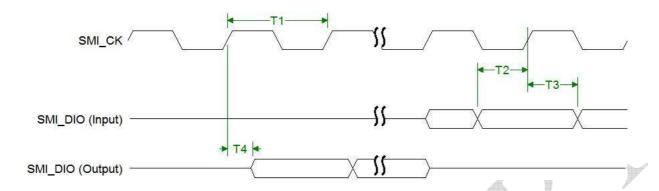

| 8.4.6    | Host SMI Interface Timing                                        | 141 |

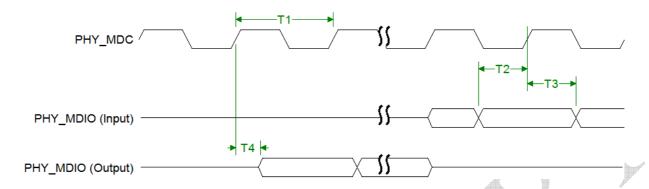

| 8.4.7    | PHY SMI Interface Timing                                         | 142 |

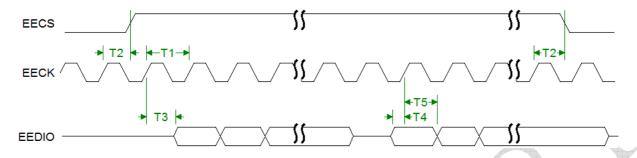

| 8.4.8    | EEPROM Timing                                                    | 143 |

| 9. Appl  | ication Information                                              | 144 |

| 9.1      | Application of GMII/MII MAC to PHY                               | 144 |

| 9.2      | Application of GMII MAC to MAC                                   | 144 |

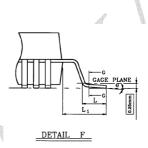

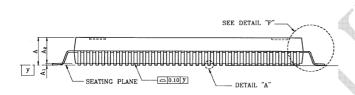

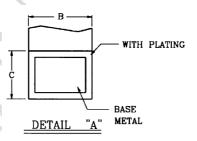

| 10. Pack | age Information                                                  | 145 |

| 11 Ordo  | aring Information                                                | 116 |

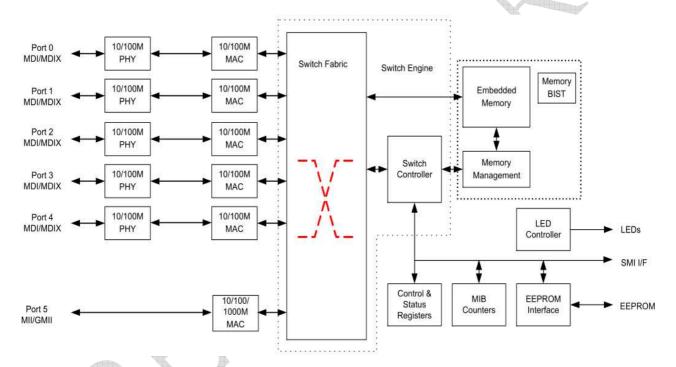

#### 1. General Description

The DM8806 is a fully integrated and cost-effective industrial-temperature (DM8806l only) fast Ethernet switch controller with five 10/100Mb PHY, five 10/100Mb MAC plus one 10/100/1000Mb MAC, and one MII/GMII interface option for 6th MAC.

The controller provides basic Layer-2 switch functions and advance IEEE 802.1Q VLAN, priority queuing scheme, IEEE 802.3az Energy Efficient Ethernet, IGMP snooping protocol, Spanning Tree protocol. The integrated 5 ports PHY are compliant with IEEE 802.3u standards. The MII/GMII interface provides the flexibility to connect Ethernet 10/100/1000Mb PHY devices.

#### 2. Block Diagram

#### 3. Features

- Ethernet Switch Ports:

- o Five 10/100Mb PHY built-in, that can be used for Copper or Fiber application

- Port 5 support MII/GMII interface to MAC

- Supports auto crossover function HP Auto-MDIX

- Supports auto-polarity for 10Mbps

- Supports Store-and-Forward and Cut-Through switching approach

- Supports up to 2K accessible MAC address table

- Automatic aging scheme

- Flow control fully supported:

- o IEEE 802.3x flow control in full-duplex mode

- Back Pressure flow control in half-duplex mode

- Supports packet length up to 1536 (default)/1552/1800/2032 bytes

- Supports bandwidth control. Ingress and egress rate limit on each port

- Supports broadcast storming filter function for broadcast, multicast and unknown unicast packets

- Supports source address filtering

- Supports high performance QoS function on each port:

- 4-level priority queues

- Two types queue scheduling: Weighted Round Robin(WRR) and Strict Priority(SP)

- o Port-based, 802.1p, IPv6 ToS Priority

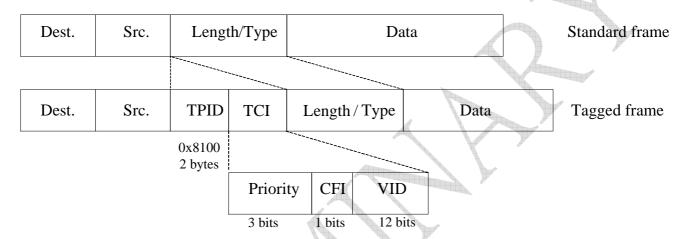

- Supports up to 16 VLAN groups:

- 802.1Q port-base and tag-based VLAN

- Full 12-bit VID, 4-bit FID

- Shared VLAN Learning (SVL) and Independent VLAN Learning (IVL)

- VLAN tag Insert/Remove function

- Leaky VLAN for unicast packets

- VLAN priority replace function

- Supports double tag (QinQ)

- Supports trunk ports

- Supports port-based and MAC-based mirror

- Supports hardware IGMP v1,v2 Snooping

- Supports hardware MLD v1 Snooping

- Supports IEEE 802.3az Energy Efficient Ethernet (EEE)

- Supports Link Fault Pass-through (LFP) and Far End Fault (FEF)

- Supports spanning tree function:

- o IEEE 802.1D Spanning Tree Protocol (STP)

- o IEEE 802.1w Rapid STP (RSTP)

- o IEEE 802.1s Multiple STP (MSTP)

- Supports 802.1x security function

- Supports WOL standby mode

- Supports optional EEPROM interface for configuration

- Supports 64-bit MIB counters for diagnostic

- Supports Serial Management Interface (SMI) for programming and diagnostics

- Supports interrupt pin for CPU application

- Supports special tag to carry control and status between Switch and CPU

- Supports four type LED display mode

- Commercial temperature range: -0°C to +70°C

- Industrial temperature range: -40°C to +85°C

- 25MHz Crystal

- 3.3V I/O with 5V tolerant

- 0.18um technology, 1.8/3.3V power supply

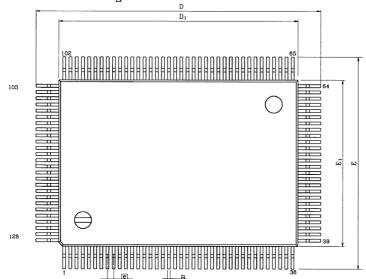

- 128-pin QFP package

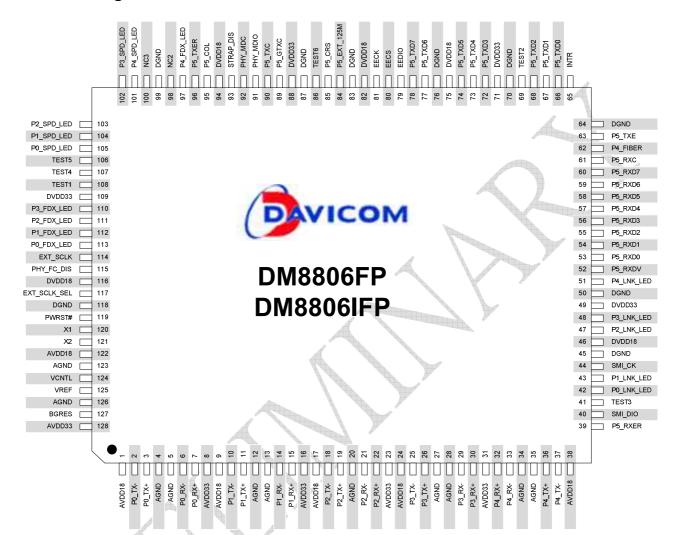

#### 4. Pin Configuration

#### 4.1 Pin Diagram

### 4.2 Pin Description

Buffer type:

I = Input,

I/O = Input / Output,

ANA = Analog,

PU = Internal pull-up (about 50K Ohm),

PUR= Internal pull-up during PWRST# period,

# = Asserted Low

O = Output,

O/D = Open Drain,

P = Power,

PD = Internal pull-down,

PDR = Internal pull-down during PWRST# period,

#### **4.2.1 LED Pins**

|         | LDTIIIS    |                |    |                                                                                                                                                                         |

|---------|------------|----------------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No. | Pin Name   | Buffer<br>Type | VO | Description                                                                                                                                                             |

| 42      | P0_LNK_LED | PU<br>6mA      | 0  | PHY 0 LED (output after reset) LED behavior can be configurable, see the LED Control Register 317h. By default, this pin is used to indicate Port 0 Link/Active status. |

| 105     | P0_SPD_LED | PDR<br>6mA     | 0  | PHY 0 LED (output after reset) LED behavior can be configurable, see the LED Control Register 317h. By default, this pin is used to indicate Port 0 Speed status.       |

| 113     | P0_FDX_LED | PDR<br>6mA     | 0  | PHY 0 LED (output after reset) LED behavior can be configurable, see the LED Control Register 317h. By default, this pin is used to indicate Port 0 Duplex status.      |

| 43      | P1_LNK_LED | PUR<br>6mA     | 0  | PHY 1 LED (output after reset) LED behavior can be configurable, see the LED Control Register 317h. By default, this pin is used to indicate Port 1 Link/Active status. |

| 104     | P1_SPD_LED | PDR<br>6mA     | 0  | PHY 1 LED (output after reset) LED behavior can be configurable, see the LED Control Register 317h. By default, this pin is used to indicate Port 1 Speed status.       |

| 112     | P1_FDX_LED | PDR<br>6mA     | 0  | PHY 1 LED (output after reset) LED behavior can be configurable, see the LED Control Register 317h. By default, this pin is used to indicate Port 1 Duplex status.      |

| 47      | P2_LNK_LED | PUR<br>6mA     | 0  | PHY 2 LED (output after reset) LED behavior can be configurable, see the LED Control Register 317h. By default, this pin is used to indicate Port 2 Link/Active status. |

| 103     | P2_SPD_LED | PDR<br>6mA     | 0  | PHY 2 LED (output after reset) LED behavior can be configurable, see the LED Control Register 317h. By default, this pin is used to indicate Port 2 Speed status.       |

| 111     | P2_FDX_LED | PDR<br>6mA     | 0  | PHY 2 LED (output after reset) LED behavior can be configurable, see the LED Control Register 317h. By default, this pin is used to indicate Port 2 Duplex status.      |

| 48      | P3_LNK_LED | PUR<br>6mA     | 0  | PHY 3 LED (output after reset) LED behavior can be configurable, see the LED Control Register 317h. By default, this pin is used to indicate Port 3 Link/Active status. |

## 6-Port 10/100Mb Fast Ethernet Smart Switch

| 102 | P3_SPD_LED | PDR<br>6mA | 0 | PHY 3 LED (output after reset) LED behavior can be configurable, see the LED Control Register 317h. By default, this pin is used to indicate Port 3 Speed status.       |

|-----|------------|------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 110 | P3_FDX_LED | PDR<br>6mA | 0 | PHY 3 LED (output after reset) LED behavior can be configurable, see the LED Control Register 317h. By default, this pin is used to indicate Port 3 Duplex status.      |

| 51  | P4_LNK_LED | PUR<br>6mA | 0 | PHY 4 LED (output after reset) LED behavior can be configurable, see the LED Control Register 317h. By default, this pin is used to indicate Port 4 Link/Active status. |

| 101 | P4_SPD_LED | PDR<br>6mA | 0 | PHY 4 LED (output after reset) LED behavior can be configurable, see the LED Control Register 317h. By default, this pin is used to indicate Port 4 Speed status.       |

| 97  | P4_FDX_LED | PDR<br>6mA | 0 | PHY 4 LED (output after reset) LED behavior can be configurable, see the LED Control Register 317h. By default, this pin is used to indicate Port 4 Duplex status.      |

### 4.2.2 **EEPROM Interface**

| Pin No. | Pin Name | Buffer<br>Type | VO | Description                                           |

|---------|----------|----------------|----|-------------------------------------------------------|

| 79      | EEDIO    | PD<br>4mA      | VO | EEPROM Data In/Output Drive/Read data to/from EEPROM  |

| 81      | EECK     | PDR<br>4mA     | 0  | EEPROM Serial Clock Drive clock to EEPROM             |

| 80      | EECS     | PD<br>4mA      | 0  | EEPROM Chip Selection. Drive chip selection to EEPROM |

### 4.2.3 Clock Interface

| Pin No. | Pin Name | Buffer<br>Type | VO | Description                                                                                    |

|---------|----------|----------------|----|------------------------------------------------------------------------------------------------|

| 120     | X1       | ANA            | I  | 25 MHz Crystal /Oscillator Input<br>Variation is limited to +/- 50 ppm.                        |

| 121     | X2       | ANA            | 0  | 25 MHz Crystal Output When X1 is connected to oscillator, this pin should be left unconnected. |

#### 4.2.4 Network Interface

|         | Network interrace |        |     |                                                    |

|---------|-------------------|--------|-----|----------------------------------------------------|

| Pin No. | Pin Name          | Buffer | VO  | Description                                        |

|         |                   | Type   |     |                                                    |

| 2       | P0_TX-            | ANA    | I/O | Port 0 TP TX                                       |

| 3       | P0_TX+            |        |     | These two pins are the Twisted Pair transmit in    |

|         |                   |        |     | MDI mode or receive in MDIX mode.                  |

| 6       | P0_RX-            | ANA    | I/O | Port 0 TP RX                                       |

| 7       | P0_RX+            |        |     | These two pins are the Twisted Pair receive in     |

|         |                   |        |     | MDI mode or transmit in MDIX mode.                 |

| 10      | P1_TX-            | ANA    | I/O | Port 1 TP TX                                       |

| 11      | P1_TX+            |        |     | These two pins are the Twisted Pair transmit in    |

|         |                   |        |     | MDI mode or receive in MDIX mode.                  |

| 14      | P1_RX-            | ANA    | I/O | Port 1 TP RX                                       |

| 15      | P1_RX+            |        |     | These two pins are the Twisted Pair receive in     |

|         |                   |        |     | MDI mode or transmit in MDIX mode.                 |

| 18      | P2_TX-            | ANA    | I/O | Port 2 TP TX                                       |

| 19      | P2_TX+            |        |     | These two pins are the Twisted Pair transmit in    |

|         |                   |        |     | MDI mode or receive in MDIX mode.                  |

| 21      | P2_RX-            | ANA    | I/O | Port 2 TP RX                                       |

| 22      | P2_RX+            |        |     | These two pins are the Twisted Pair receive in     |

|         |                   |        |     | MDI mode or transmit in MDIX mode.                 |

| 25      | P3_TX-            | ANA    | I/O | Port 3 TP TX                                       |

| 26      | P3_TX+            |        |     | These two pins are the Twisted Pair transmit in    |

|         |                   |        |     | MDI mode or receive in MDIX mode.                  |

| 29      | P3_RX-            | ANA    | 1/0 | Port 3 TP RX                                       |

| 30      | P3_RX+            |        |     | These two pins are the Twisted Pair receive in     |

|         | 5                 |        |     | MDI mode or transmit in MDIX mode.                 |

| 32      | P4_RX+            | ANA    | I/O | Port 4 TP RX                                       |

| 33      | P4_RX-            |        |     | These two pins are the Twisted Pair transmit in    |

| 00      | D.( T)/           | 2212   | 1/0 | MDI mode or receive in MDIX mode.                  |

| 36      | P4_TX+            | ANA    | I/O | Port 4 TP TX                                       |

| 37      | P4_TX-            |        |     | These two pins are the Twisted Pair receive in     |

| 407     | DODEO             | 0.010  | 1/0 | MDI mode or transmit in MDIX mode.                 |

| 127     | BGRES             | ANA    | I/O | Bandgap Pin                                        |

|         |                   |        |     | Connect a 6.8K±1% precision resistor to AGND in    |

| 124     | VONT              | 0.010  | 1/0 | application.                                       |

| 124     | VCNTL             | ANA    | I/O | 1.8V Voltage control to control external BJT       |

| 125     | VREF              | ANA    | 0   | Voltage Reference                                  |

|         |                   | 7      |     | Connect a 0.1u capacitor to ground in application. |

Preliminary Doc No: DM8806/DM8806I – M2A-DS-P01 January 18, 2013

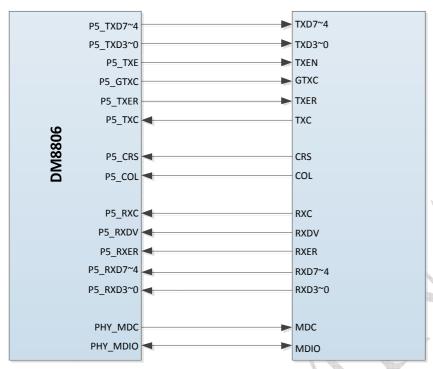

### 4.2.5 Port 5 GMII/MII Interface

Port 5 works under GMII interface when it is linked at 1G, and it works under MII interface when it is linked at 10/100M.

#### **Port 5 GMII Pins**

| Pin No. | Pin Name | Buffer | VO.        | Description             |

|---------|----------|--------|------------|-------------------------|

|         |          | Туре   |            | F                       |

| 78      | P5_TXD7  | PDR    | 0          | Transmit Data High Bits |

| 77      | P5_TXD6  | 4mA    |            | A                       |

| 74      | P5_TXD5  |        |            |                         |

| 73      | P5_TXD4  |        |            |                         |

| 72      | P5_TXD3  | PDR    | 0          | Transmit Data Low Bits  |

| 68      | P5_TXD2  | 4mA    |            |                         |

| 67      | P5_TXD1  |        |            |                         |

| 66      | P5_TXD0  |        |            |                         |

| 63      | P5_TXE   | PDR    | 0          | Transmit Enable         |

|         |          | 4mA    |            |                         |

| 89      | P5_GTXC  | PD     | 0          | GMII Transmit Clock     |

|         |          | 4mA    |            |                         |

| 96      | P5_TXER  | PDR    | 0          | Transmit Data Error     |

|         |          | 4mA    |            |                         |

| 85      | P5_CRS   | -      | I          | Carrier Sense           |

| 95      | P5_COL   | PDR    |            | Collision Detect.       |

| 61      | P5_RXC   | PDR    |            | Receive Clock           |

| 52      | P5_RXDV  | PD     | <b>4</b> 1 | Receive Data Valid      |

| 39      | P5_RXER  | PD     |            | Receive Data Error      |

| 60      | P5_RXD7  | PDR    | 11         | Receive Data High Bits  |

| 59      | P5_RXD6  | 4      | 1 4        |                         |

| 58      | P5_RXD5  |        | A          |                         |

| 57      | P5_RXD4  | 4      |            |                         |

| 56      | P5_RXD3  | PD     | I          | Receive Data Low Bits   |

| 55      | P5_RXD2  |        |            |                         |

| 54      | P5_RXD1  |        |            |                         |

| 53      | P5_RXD0  |        |            |                         |

Preliminary

Doc No: DM8806/DM8806I – M2A-DS-P01

January 18, 2013

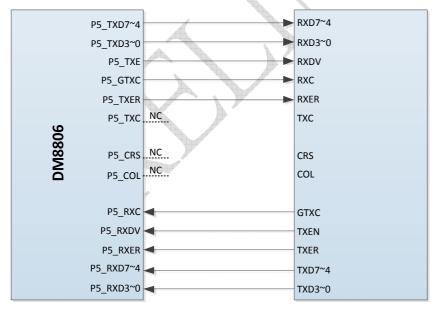

#### **Port 5 MII Pins**

| Pin No. | Pin Name | Buffer | VO | Description         |

|---------|----------|--------|----|---------------------|

|         |          | Type   |    |                     |

| 72      | P5_TXD3  | PDR    | 0  | Transmit Data Bits  |

| 68      | P5_TXD2  | 4mA    |    |                     |

| 67      | P5_TXD1  |        |    |                     |

| 66      | P5_TXD0  |        |    |                     |

| 63      | P5_TXE   | PDR    | 0  | Transmit Enable     |

|         |          | 4mA    |    |                     |

| 96      | P5_TXER  | PDR    | 0  | Transmit Data Error |

|         |          | 4mA    |    |                     |

| 90      | P5_TXC   | PD     | I  | Transmit Clock.     |

| 85      | P5_CRS   | -      | I  | Carrier Sense       |

| 95      | P5_COL   | PDR    | I  | Collision Detect.   |

| 61      | P5_RXC   | PDR    | ı  | Receive Clock       |

| 52      | P5_RXDV  | PD     | I  | Receive Data Valid  |

| 39      | P5_RXER  | PD     | I  | Receive Data Error  |

| 56      | P5_RXD3  | PD     | I  | Receive Data Bits   |

| 55      | P5_RXD2  |        |    |                     |

| 54      | P5_RXD1  |        |    |                     |

| 53      | P5_RXD0  |        |    |                     |

### 4.2.6 Miscellaneous Pins

| Pin No. | Pin Name     | Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | VO                       | Description                                      |

|---------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------------------|

|         |              | Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          | ·                                                |

| 40      | SMI_DIO      | PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I/O                      | Serial Management Data Input/output as CPU       |

|         |              | 4mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                          | interface                                        |

| 44      | SMI_CK       | PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I                        | Serial Management Data Clock as CPU interface    |

| 91      | PHY_MDIO     | PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I/O                      | MII Serial Management Data Input/output as       |

|         |              | 4mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                          | External PHY interface                           |

| 92      | PHY_MDC      | PDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                        | MII Serial Management Data Clock as External     |

|         |              | 4mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                        | PHY interface                                    |

| 65      | INTR         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                        | Interrupt signals to external CPU                |

| 00      | OTD AD DIO   | 4mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                          | D .                                              |

| 93      | STRAP_DIS    | PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I                        | Reserved                                         |

| 86      | TEST6        | PU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                        | Tie STRAP_DIS to ground in application Test pins |

| 106     | TEST5        | PDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | I                        | Tie TEST6, TEST5 and TEST4 to ground in          |

| 107     | TEST4        | PDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                          | application                                      |